# Chrontel

# CH7026 TV/VGA Encoder

# **FEATURES**

- Support multiple output formats. Such as SDTV format (NTSC and PAL), HDTV format for 480p,576p,720p and 1080i, analog RGB output for VGA. Sync signals can be provided in separated or composite manner (Programmable composite sync generation).

- Three on-chip 10-bit high speed DACs providing flexible output capabilities. Such as single, double or triple CVBS outputs, YPbPr output, RGB output and simultaneous CVBS and S-video outputs.

- Internal embedded 16Mbits SDRAM is used as frame buffer. Supporting for frame rate conversion. 90/180/270 degree image rotation and vertical or horizontal flip functions are supported.

- Programmable 24-bit/18-bit/16-bit/15-bit/12-bit/8-bit digital input interface supports various RGB (RGB888, RGB666, RGB565 and etc), YCbCr (4:4:4 YCbCr, ITU656) and 2x or 3x multiplexed input. CPU/Memory interface are supported.

- Support for flexible input resolution is up to 800x800 and 1024x680. 320x240, 640x480, 960x720 are support.

- Bypass mode is supported.

- Flexible up and down scaling engine is embedded including de-flickering capability. Text enhancement is supported.

- Pixel by pixel brightness, contrast, hue and saturation adjustment for each kind of output are supported. For RGB output, only brightness and contrast adjustment are supported.

- Pixel by pixel horizontal position adjustment and line by line vertical position adjustment are supported.

- Fully programmable through serial port. IO and SPC/SPD voltage supported is from 1.2V to 3.3V.

- TV/Monitor connection detect capability.

- Programmable power management. DAC can be switched off based on detection result (Driver support is required).

- Flexible pixel clock frequency from graphics controller is supported (2.3MHz –120MHz). Flexible input clock from crystal or oscillator is supported (2.3MHz 64MHz).

- Offered in QFP package.

# **GENERAL DESCRIPTION**

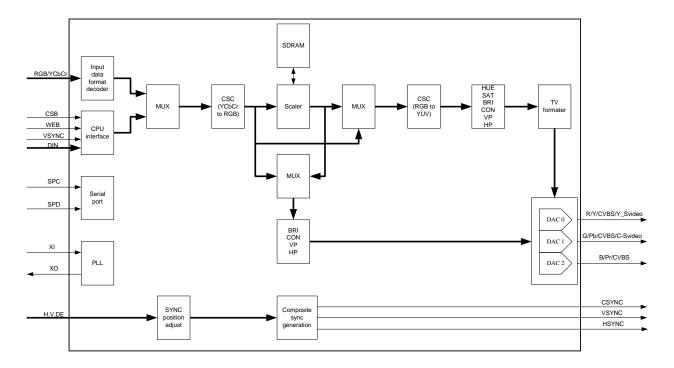

The CH7026 is a device targeting handheld and similar consumer systems which accept digital input signal. CH7026 encodes and transmits data through 10-bit DACs. The device is able to encode the video signals and generate synchronization signals SDTV format for NTSC and PAL standards and HDTV format for 480p,576p,720p and 1080i. Analog RGB output and composite SYNC signal are also supported. The device accepts different data formats including RGB and YCbCr (e.g. RGB565, RGB888, ITU656 like YCbCr, etc.).Both interlaced and non-interlaced input data formats are supported. 16Mbit SDRAM is embedded in package. Frame rate conversion, Image rotation, zooming and scaling, are supported.

Note: the above feature list is subject to change without notice. Please contact Chrontel for more information and current updates.

Figure 1: CH7026 Block Diagram

# **TABLE OF CONTENTS**

| GENERAL DESCRIPTION.       1         1.0       PIN-OUT.         5       1.1         1.1       Package Diagram         5       1.2         Pin Description       6         2.0       FUNCTIONAL DESCRIPTION         8       2.1         1.1       Input Interface.         8       2.1.1         1.1       Input Olock and Data Timing Diagram         8       2.1.2         1.1       Input Clock and Data Timing Diagram         8       2.1.3         1.1       Input Data Voltage         9       2.1.4         1.1       2.2.1         2.2       Chip Output         2.1       Input Data Format.         2.2       Video DAC Output         11       2.2.2         2.2.3       Video DAC Councetion Detect         2.2.4       DAC Connection Detect         2.2.5       Video DAC Connection Detect         2.2.6       Picture Enhancement         2.2.7       Color Sub-carrier Generation         2.3       Test Patern Select         3.3.1       Test Patern Select         3.3.2       SDRAM Power Down         3.4                                                                                                                                                   | FEA | TURES | 5                                                 | 1  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|---------------------------------------------------|----|

| 1.1       Package Diagram       .5         1.2       Pin Description       .6         2.0       FUNCTIONAL DESCRIPTION       .8         2.1.1       Input Interface.       .8         2.1.1       Overview.       .8         2.1.2       Input Clock and Data Timing Diagram       .8         2.1.3       Input Data Voltage.       .9         2.1.4       Input Data Format.       .9         2.2       Chip Output       .11         2.2.2       Video DAC Output       .12         2.2.3       Video DAC Output       .12         2.2.4       DAC Single/Double Termination       .12         2.2.5       Video DAC Conctroin Detect       .12         2.2.6       Picture Enhancement       .12         2.2.7       Color Sub-carrier Generation       .12         2.2.8       TU-R BT.470 Compliance       .13         2.3.1       Test Pattern Select       .13         2.3.2       SDRAM Power Down       .13         2.4       Serial Port       .13         2.4.5       Electrical Characteristics of the Serial Port       .14         2.4.3       Transfer Protocol       .14         2.4.4       Chrontel Enco                                                        | GEI | NERAL | DESCRIPTION                                       | 1  |

| 1.1       Package Diagram       .5         1.2       Pin Description       .6         2.0       FUNCTIONAL DESCRIPTION       .8         2.1.1       Input Interface.       .8         2.1.1       Overview.       .8         2.1.2       Input Clock and Data Timing Diagram       .8         2.1.3       Input Data Voltage.       .9         2.1.4       Input Data Format.       .9         2.2       Chip Output       .11         2.2.2       Video DAC Output       .12         2.2.3       Video DAC Output       .12         2.2.4       DAC Single/Double Termination       .12         2.2.5       Video DAC Conctroin Detect       .12         2.2.6       Picture Enhancement       .12         2.2.7       Color Sub-carrier Generation       .12         2.2.8       TU-R BT.470 Compliance       .13         2.3.1       Test Pattern Select       .13         2.3.2       SDRAM Power Down       .13         2.4       Serial Port       .13         2.4.5       Electrical Characteristics of the Serial Port       .14         2.4.3       Transfer Protocol       .14         2.4.4       Chrontel Enco                                                        | 1.0 |       | PIN-OUT                                           | 5  |

| 1.2       Pin Description       6         2.0       FUNCTIONAL DESCRIPTION       8         2.1       Input Interface       8         2.1.1       Overview       8         2.1.1       Overview       8         2.1.1       Overview       8         2.1.1       Input Clock and Data Timing Diagram       8         2.1.2       Input Data Voltage       9         2.1.4       Input Data Format       9         2.2       Chip Output       11         2.2.2       Video DAC Output       12         2.2.4       DAC Single/Double Termination       12         2.2.5       Video DAC Connection Detect       12         2.2.6       Picture Enhancement       12         2.2.7       Color Sub-carrier Generation       12         2.2.8       ITU-R BT 470 Compliance       13         2.3.1       Test Pattern Select       13         2.3.2       SDRAM Power Down       13         2.4.1       Introduction       13         2.4.2       Electrical Characteristics of the Serial Port       14         2.4.3       Transfer Protocol       14         2.4.4       Chrontel Encoder Write Cycle Protocol (R/W* = 0)<                                                        | 1.0 | 1.1   |                                                   |    |

| 2.1       Input Interface       8         2.1.1       Overview       8         2.1.2       Input Clock and Data Timing Diagram       8         2.1.3       Input Data Voltage       9         2.1       Input Data Format       9         2.2       Chip Output       11         2.1.1       TV Output       11         2.2       VGA Output       11         2.2.2       VGA Output       12         2.3       Video DAC Output       12         2.2.4       DAC Single/Double Termination       12         2.2.5       Video DAC Connection Detect       12         2.2.6       Picture Enhancement       12         2.2.7       Color Sub-carrier Generation       12         2.2.8       ITU-R BT.470 Compliance       13         2.3.1       Test BT.470 Compliance       13         2.3.2       SDRAM Power Down       13         2.4.1       Introduction       13         2.4.2       Serial Port       13         2.4.1       Introduction       13         2.4.2       Electrical Characteristics of the Serial Port       14         2.4.3       Tarasfer Protocol       14                                                                                            |     |       |                                                   |    |

| 2.1       Input Interface       8         2.1.1       Overview       8         2.1.2       Input Clock and Data Timing Diagram       8         2.1.3       Input Data Voltage       9         2.1       Input Data Format       9         2.2       Chip Output       11         2.1.1       TV Output       11         2.2       VGA Output       11         2.2.2       VGA Output       12         2.3       Video DAC Output       12         2.2.4       DAC Single/Double Termination       12         2.2.5       Video DAC Connection Detect       12         2.2.6       Picture Enhancement       12         2.2.7       Color Sub-carrier Generation       12         2.2.8       ITU-R BT.470 Compliance       13         2.3.1       Test BT.470 Compliance       13         2.3.2       SDRAM Power Down       13         2.4.1       Introduction       13         2.4.2       Serial Port       13         2.4.1       Introduction       13         2.4.2       Electrical Characteristics of the Serial Port       14         2.4.3       Tarasfer Protocol       14                                                                                            |     |       |                                                   |    |

| 2.1.1       Overview       8         2.1.2       Input Clock and Data Timing Diagram       8         2.1.3       Input Data Voltage       9         2.1.4       Input Data Format       9         2.2       Chip Output       11         2.2.1       TV Output       11         2.2.2       VGA Output       11         2.2.1       Video DAC Output       12         2.2.2       VGA Output       12         2.2.3       Video DAC Connection Detect       12         2.2.4       DAC Single/Double Termination       12         2.2.5       Video DAC Comection Detect       12         2.2.6       Picture Enhancement       12         2.2.7       Color Sub-carrier Generation       12         2.2.8       ITU-R BT 470 Compliance       13         2.3.1       Testing Functions and Power Down Mode       13         2.3.2       SDRAM Power Down       13         2.4.1       Introduction       13         2.4.2       Berial Port       13         2.4.3       Transfer Protocol       14         2.4.4       Chrontel Encoder Write Cycle Protocol (R/W* = 0)       15         2.4.5       Chrontel Encoder Re                                                        | 2.0 |       |                                                   |    |

| 2.1.2       Input Clock and Data Timing Diagram.       8         2.1.3       Input Data Voltage.       9         2.1.4       Input Data Format.       9         2.1.4       Input Data Format.       9         2.2       Chip Output.       11         2.2.1       TV Output.       12         2.2.3       Video DAC Output.       12         2.2.4       DAC Single/Double Termination       12         2.2.5       Video DAC Connection Detect       12         2.2.6       Picture Enhancement       12         2.2.7       Color Sub-carrier Generation       12         2.2.8       ITU-R BT.470 Compliance       13         2.3.1       Testing Functions and Power Down Mode       13         2.3.1       Test Pattern Select       13         2.3.2       SDRAM Power Down       13         2.4.1       Introduction       13         2.4.2       Electrical Characteristics of the Serial Port       14         2.4.3       Transfer Protocol       14         2.4.4       Chrontel Encoder Write Cycle Protocol (R/W* = 0)       15         2.4.5       Chrontel Encoder Read Cycle Protocol (R/W* = 1)       16         3.0       ELECTRICAL SPECIFICATIONS            |     |       |                                                   |    |

| 2.1.3       Input Data Voltage       9         2.1.4       Input Data Format       9         2.2       Chip Output       11         2.2.1       TV Output       11         2.2.2       VGA Output       12         2.2.3       Video DAC Output       12         2.2.4       DAC Single/Double Termination       12         2.2.5       Video DAC Connection Detect       12         2.2.6       Picture Enhancement       12         2.2.7       Color Sub-carrier Generation       12         2.2.8       ITU-R BT 470 Compliance       13         2.3.1       Testing Functions and Power Down Mode       13         2.3.2       SDRAM Power Down       13         2.4.1       Introduction       13         2.4.2       Electrical Characteristics of the Serial Port       14         2.4.3       Transfer Protocol       14         2.4.4       Chrontel Encoder Read Cycle Protocol (R/W* = 0)       15         2.4.5       Chrontel Encoder Read Cycle Protocol (R/W* = 1)       16         3.0 <b>ELECTRICAL SPECIFICATIONS</b> 18         3.1       Absolute Maximum Ratings       18         3.2       Recommended Operating Conditions       <                        |     |       |                                                   |    |

| 2.1.4       Input Data Format       9         2.2       Chip Output       11         2.2.1       TV Output       11         2.2.2       VGA Output       11         2.2.1       TV Output       11         2.2.2       VGA Output       11         2.2.3       Video DAC Output       12         2.2.4       DAC Single/Double Termination       12         2.2.5       Video DAC Connection Detect       12         2.2.6       Picture Enhancement       12         2.2.7       Color Sub-carrier Generation       12         2.2.8       ITU-R BT 470 Compliance       13         2.3       Testing Functions and Power Down Mode       13         2.3.1       Test Pattern Select       13         2.3.2       SDRAM Power Down       13         2.4.3       Transfer Protocol       13         2.4.4       Chrontel Encoder Write Cycle Protocol (R/W* = 0)       15         2.4.5       Chrontel Encoder Read Cycle Protocol (R/W* = 1)       16         3.0       ELECTRICAL SPECIFICATIONS       18         3.1       Absolute Maximum Ratings       18         3.2       Recommended Operating Conditions       18 <td< th=""><th></th><td></td><td></td><td></td></td<> |     |       |                                                   |    |

| 2.2       Chip Output       11         2.2.1       TV Output       11         2.2.2       VGA Output       12         2.2.3       Video DAC Output       12         2.2.4       DAC Single/Double Termination       12         2.2.5       Video DAC Connection Detect       12         2.2.6       Picture Enhancement       12         2.2.7       Color Sub-carrier Generation       12         2.2.8       ITU-R BT-470 Compliance       13         2.3       Testing Functions and Power Down Mode       13         2.3.1       Test Pattern Select       13         2.3.2       SDRAM Power Down       13         2.4.4       Serial Port       13         2.4.5       Chrontel Encoder Write Cycle Protocol (R/W* = 0)       15         2.4.6       Chrontel Encoder Read Cycle Protocol (R/W* = 1)       16         3.0       ELECTRICAL SPECIFICATIONS       18         3.1       Absolute Maximum Ratings       18         3.3       Electrical Characteristics       19         3.4       Digital Inputs / Outputs       19         3.5       AC Specifications       20                                                                                               |     |       |                                                   |    |

| 2.2.1       TV Output       11         2.2.2       VGA Output       12         2.2.3       Video DAC Output       12         2.2.4       DAC Single/Double Termination       12         2.2.5       Video DAC Connection Detect       12         2.2.6       Picture Enhancement       12         2.2.7       Color Sub-carrier Generation       12         2.2.8       ITU-R BT.470 Compliance       13         2.3       Testing Functions and Power Down Mode       13         2.3.1       Test Pattern Select       13         2.3.2       SDRAM Power Down       13         2.4.4       Serial Port       13         2.4.5       Electrical Characteristics of the Serial Port       14         2.4.3       Transfer Protocol       14         2.4.4       Chrontel Encoder Write Cycle Protocol (R/W* = 0)       15         2.4.5       Chrontel Encoder Write Cycle Protocol (R/W* = 1)       16         3.0       ELECTRICAL SPECIFICATIONS       18         3.1       Absolute Maximum Ratings       18         3.3       Electrical Characteristics       19         3.4       Digital Inputs / Outputs       19         3.5       AC Specifications                    |     |       |                                                   |    |

| 2.2.2       VGA Output       12         2.2.3       Video DAC Output       12         2.2.4       DAC Single/Double Termination       12         2.2.5       Video DAC Connection Detect       12         2.2.6       Picture Enhancement       12         2.2.7       Color Sub-carrier Generation       12         2.2.8       ITU-R BT 470 Compliance       13         2.3       Testing Functions and Power Down Mode       13         2.3.1       Test Pattern Select       13         2.3.2       SDRAM Power Down       13         2.4       Serial Port       13         2.4.1       Introduction       13         2.4.2       Electrical Characteristics of the Serial Port       14         2.4.3       Transfer Protocol       14         2.4.4       Chrontel Encoder Write Cycle Protocol (R/W* = 0)       15         2.4.5       Chrontel Encoder Read Cycle Protocol (R/W* = 1)       16         3.0       ELECTRICAL SPECIFICATIONS       18         3.1       Absolute Maximum Ratings       18         3.2       Recommended Operating Conditions       18         3.3       Electrical Characteristics       19         3.4       Digital Inputs /             |     |       |                                                   |    |

| 2.2.3       Video DAC Output       12         2.2.4       DAC Single/Double Termination       12         2.2.5       Video DAC Connection Detect       12         2.2.6       Picture Enhancement       12         2.2.7       Color Sub-carrier Generation       12         2.2.8       ITU-R BT.470 Compliance       13         2.3.1       Test Pattern Select       13         2.3.2       SDRAM Power Down Mode       13         2.3.1       Test Pattern Select       13         2.3.2       SDRAM Power Down       13         2.4.1       Introduction       13         2.4.2       Electrical Characteristics of the Serial Port       14         2.4.3       Transfer Protocol       14         2.4.4       Chrontel Encoder Write Cycle Protocol (R/W* = 0)       15         2.4.5       Chrontel Encoder Read Cycle Protocol (R/W* = 1)       16         3.0       ELECTRICAL SPECIFICATIONS       18         3.1       Absolute Maximum Ratings       18         3.2       Recommended Operating Conditions       18         3.3       Electrical Characteristics       19         3.4       Digital Inputs / Outputs       19         3.5       AC Specif            |     |       | 1                                                 |    |

| 2.2.4       DAC Single/Double Termination       12         2.2.5       Video DAC Connection Detect       12         2.2.6       Picture Enhancement       12         2.2.7       Color Sub-carrier Generation       12         2.2.8       ITU-R BT.470 Compliance       13         2.3.1       Testing Functions and Power Down Mode       13         2.3.1       Test Pattern Select       13         2.3.2       SDRAM Power Down       13         2.4.3       Serial Port       13         2.4.1       Introduction       13         2.4.2       Electrical Characteristics of the Serial Port       14         2.4.3       Transfer Protocol       14         2.4.4       Chrontel Encoder Write Cycle Protocol (R/W* = 0)       15         2.4.5       Chrontel Encoder Read Cycle Protocol (R/W* = 1)       16         3.0       ELECTRICAL SPECIFICATIONS       18         3.1       Absolute Maximum Ratings       18         3.2       Recommended Operating Conditions       18         3.3       Electrical Characteristics       19         3.4       Digital Inputs / Outputs       19         3.5       AC Specifications       20         4.0       PA            |     |       | 1                                                 |    |

| 2.2.5       Video DAC Connection Detect       12         2.2.6       Picture Enhancement       12         2.2.7       Color Sub-carrier Generation       12         2.2.8       ITU-R BT.470 Compliance       13         2.3       Testing Functions and Power Down Mode       13         2.3.1       Test Pattern Select       13         2.3.2       SDRAM Power Down       13         2.4.3       Serial Port       13         2.4.4       Serial Port       13         2.4.2       Electrical Characteristics of the Serial Port       14         2.4.3       Transfer Protocol       14         2.4.4       Chrontel Encoder Write Cycle Protocol (R/W* = 0)       15         2.4.5       Chrontel Encoder Read Cycle Protocol (R/W* = 1)       16         3.0       ELECTRICAL SPECIFICATIONS       18         3.1       Absolute Maximum Ratings       18         3.2       Recommended Operating Conditions       18         3.3       Electrical Characteristics       19         3.4       Digital Inputs / Outputs       19         3.5       AC Specifications       20                                                                                               |     |       |                                                   |    |

| 2.2.6       Picture Enhancement       12         2.2.7       Color Sub-carrier Generation       12         2.2.8       ITU-R BT.470 Compliance       13         2.3       Testing Functions and Power Down Mode       13         2.3       Test Pattern Select       13         2.3.1       Test Pattern Select       13         2.3.2       SDRAM Power Down       13         2.4       Serial Port       13         2.4.1       Introduction       13         2.4.2       Electrical Characteristics of the Serial Port       14         2.4.3       Transfer Protocol       14         2.4.4       Chrontel Encoder Write Cycle Protocol (R/W* = 0)       15         2.4.5       Chrontel Encoder Read Cycle Protocol (R/W* = 1)       16         3.0       ELECTRICAL SPECIFICATIONS       18         3.1       Absolute Maximum Ratings       18         3.2       Recommended Operating Conditions       18         3.3       Electrical Characteristics       19         3.4       Digital Inputs / Outputs       19         3.5       AC Specifications       20         4.0       PACKAGE DIMENSIONS       21                                                            |     |       |                                                   |    |

| 2.2.7       Color Sub-carrier Generation       12         2.2.8       ITU-R BT.470 Compliance       13         2.3       Testing Functions and Power Down Mode       13         2.3       Testing Functions and Power Down Mode       13         2.3.1       Test Pattern Select       13         2.3.2       SDRAM Power Down       13         2.4.3       Serial Port       13         2.4.1       Introduction       13         2.4.2       Electrical Characteristics of the Serial Port       14         2.4.3       Transfer Protocol       14         2.4.4       Chrontel Encoder Write Cycle Protocol (R/W* = 0)       15         2.4.5       Chrontel Encoder Read Cycle Protocol (R/W* = 1)       16         3.0       ELECTRICAL SPECIFICATIONS       18         3.1       Absolute Maximum Ratings       18         3.2       Recommended Operating Conditions       18         3.3       Electrical Characteristics       19         3.4       Digital Inputs / Outputs       19         3.5       AC Specifications       20         4.0       PACKAGE DIMENSIONS       21                                                                                         |     |       |                                                   |    |

| 2.2.8       ITU-R BT.470 Compliance       13         2.3       Testing Functions and Power Down Mode       13         2.3.1       Test Pattern Select       13         2.3.2       SDRAM Power Down       13         2.4       Serial Port       13         2.4.1       Introduction       13         2.4.2       Electrical Characteristics of the Serial Port       14         2.4.3       Transfer Protocol       14         2.4.4       Chrontel Encoder Write Cycle Protocol (R/W* = 0)       15         2.4.5       Chrontel Encoder Read Cycle Protocol (R/W* = 1)       16 <b>3.0 ELECTRICAL SPECIFICATIONS</b> 18         3.1       Absolute Maximum Ratings       18         3.2       Recommended Operating Conditions       18         3.3       Electrical Characteristics       19         3.4       Digital Inputs / Outputs       19         3.5       AC Specifications       20 <b>4.0 PACKAGE DIMENSIONS</b> 21                                                                                                                                                                                                                                                |     |       |                                                   |    |

| 2.3       Testing Functions and Power Down Mode       13         2.3.1       Test Pattern Select       13         2.3.2       SDRAM Power Down       13         2.4       Serial Port       13         2.4.1       Introduction       13         2.4.2       Electrical Characteristics of the Serial Port       14         2.4.3       Transfer Protocol       14         2.4.4       Chrontel Encoder Write Cycle Protocol (R/W* = 0)       15         2.4.5       Chrontel Encoder Read Cycle Protocol (R/W* = 1)       16 <b>3.0</b> ELECTRICAL SPECIFICATIONS       18         3.1       Absolute Maximum Ratings       18         3.2       Recommended Operating Conditions       18         3.3       Electrical Characteristics       19         3.4       Digital Inputs / Outputs       19         3.5       AC Specifications       20 <b>4.0</b> PACKAGE DIMENSIONS       21                                                                                                                                                                                                                                                                                         |     |       |                                                   |    |

| 2.3.1       Test Pattern Select       13         2.3.2       SDRAM Power Down       13         2.4       Serial Port       13         2.4.1       Introduction       13         2.4.2       Electrical Characteristics of the Serial Port       14         2.4.3       Transfer Protocol       14         2.4.4       Chrontel Encoder Write Cycle Protocol (R/W* = 0)       15         2.4.5       Chrontel Encoder Read Cycle Protocol (R/W* = 1)       16 <b>3.0 ELECTRICAL SPECIFICATIONS</b> 18         3.1       Absolute Maximum Ratings       18         3.2       Recommended Operating Conditions       18         3.3       Electrical Characteristics       19         3.4       Digital Inputs / Outputs       19         3.5       AC Specifications       20 <b>4.0</b> PACKAGE DIMENSIONS       21                                                                                                                                                                                                                                                                                                                                                                |     |       |                                                   |    |

| 2.3.2       SDRAM Power Down       13         2.4       Serial Port       13         2.4.1       Introduction       13         2.4.2       Electrical Characteristics of the Serial Port       14         2.4.3       Transfer Protocol       14         2.4.4       Chrontel Encoder Write Cycle Protocol (R/W* = 0)       15         2.4.5       Chrontel Encoder Read Cycle Protocol (R/W* = 1)       16 <b>3.0 ELECTRICAL SPECIFICATIONS</b> 18         3.1       Absolute Maximum Ratings       18         3.2       Recommended Operating Conditions       18         3.3       Electrical Characteristics       19         3.4       Digital Inputs / Outputs       19         3.5       AC Specifications       20 <b>4.0 PACKAGE DIMENSIONS 21</b>                                                                                                                                                                                                                                                                                                                                                                                                                       |     |       |                                                   |    |

| 2.4Serial Port132.4.1Introduction132.4.2Electrical Characteristics of the Serial Port142.4.3Transfer Protocol142.4.4Chrontel Encoder Write Cycle Protocol (R/W* = 0)152.4.5Chrontel Encoder Read Cycle Protocol (R/W* = 1)163.0ELECTRICAL SPECIFICATIONS183.1Absolute Maximum Ratings183.2Recommended Operating Conditions183.3Electrical Characteristics193.4Digital Inputs / Outputs193.5AC Specifications204.0PACKAGE DIMENSIONS21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |       |                                                   |    |

| 2.4.1Introduction132.4.2Electrical Characteristics of the Serial Port142.4.3Transfer Protocol142.4.4Chrontel Encoder Write Cycle Protocol (R/W* = 0)152.4.5Chrontel Encoder Read Cycle Protocol (R/W* = 1)163.0ELECTRICAL SPECIFICATIONS183.1Absolute Maximum Ratings183.2Recommended Operating Conditions183.3Electrical Characteristics193.4Digital Inputs / Outputs193.5AC Specifications204.0PACKAGE DIMENSIONS21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |       |                                                   |    |

| 2.4.2Electrical Characteristics of the Serial Port142.4.3Transfer Protocol142.4.4Chrontel Encoder Write Cycle Protocol (R/W* = 0)152.4.5Chrontel Encoder Read Cycle Protocol (R/W* = 1)163.0ELECTRICAL SPECIFICATIONS183.1Absolute Maximum Ratings183.2Recommended Operating Conditions183.3Electrical Characteristics193.4Digital Inputs / Outputs193.5AC Specifications204.0PACKAGE DIMENSIONS21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     | 2.4   |                                                   |    |

| 2.4.3Transfer Protocol142.4.4Chrontel Encoder Write Cycle Protocol (R/W* = 0)152.4.5Chrontel Encoder Read Cycle Protocol (R/W* = 1)163.0ELECTRICAL SPECIFICATIONS183.1Absolute Maximum Ratings183.2Recommended Operating Conditions183.3Electrical Characteristics193.4Digital Inputs / Outputs193.5AC Specifications204.0PACKAGE DIMENSIONS21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | 2.4.1 |                                                   |    |

| 2.4.4Chrontel Encoder Write Cycle Protocol (R/W* = 0)152.4.5Chrontel Encoder Read Cycle Protocol (R/W* = 1)163.0ELECTRICAL SPECIFICATIONS183.1Absolute Maximum Ratings183.2Recommended Operating Conditions183.3Electrical Characteristics193.4Digital Inputs / Outputs193.5AC Specifications204.0PACKAGE DIMENSIONS21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     | 2.4.2 |                                                   |    |

| 2.4.5Chrontel Encoder Read Cycle Protocol (R/W* = 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |       |                                                   |    |

| 3.0ELECTRICAL SPECIFICATIONS183.1Absolute Maximum Ratings183.2Recommended Operating Conditions183.3Electrical Characteristics193.4Digital Inputs / Outputs193.5AC Specifications204.0PACKAGE DIMENSIONS21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     | 2.4.4 | Chrontel Encoder Write Cycle Protocol (R/W* = 0)1 | 5  |

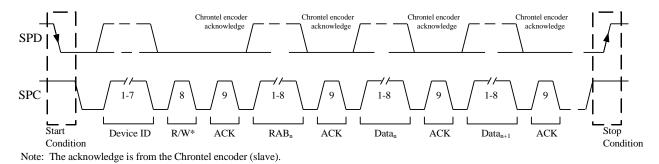

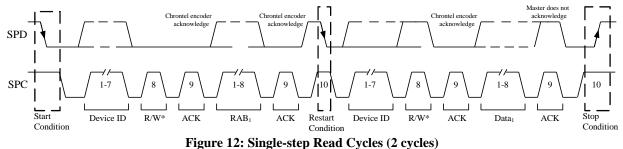

| 3.1Absolute Maximum Ratings183.2Recommended Operating Conditions183.3Electrical Characteristics193.4Digital Inputs / Outputs193.5AC Specifications204.0PACKAGE DIMENSIONS21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     | 2.4.5 | 5 Chrontel Encoder Read Cycle Protocol (R/W* = 1) | 6  |

| 3.1Absolute Maximum Ratings183.2Recommended Operating Conditions183.3Electrical Characteristics193.4Digital Inputs / Outputs193.5AC Specifications204.0PACKAGE DIMENSIONS21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3.0 |       | FLECTRICAL SPECIFICATIONS 1                       | 8  |

| 3.2Recommended Operating Conditions183.3Electrical Characteristics193.4Digital Inputs / Outputs193.5AC Specifications204.0PACKAGE DIMENSIONS21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5.0 | 31    |                                                   |    |

| 3.3       Electrical Characteristics       19         3.4       Digital Inputs / Outputs       19         3.5       AC Specifications       20         4.0       PACKAGE DIMENSIONS       21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |       |                                                   |    |

| 3.4       Digital Inputs / Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |       |                                                   |    |

| 3.5       AC Specifications       20         4.0       PACKAGE DIMENSIONS       21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |       |                                                   |    |

| 4.0 PACKAGE DIMENSIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |       |                                                   |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     | 5.5   | AC Specifications                                 | .0 |

| 5.0 REVISION HISTORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4.0 |       | PACKAGE DIMENSIONS                                | 1  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5.0 |       | REVISION HISTORY                                  | 2  |

# FIGURES AND TABLES

# LIST OF FIGURES

| Figure 1: CH7026 Block Diagram                               | 2  |

|--------------------------------------------------------------|----|

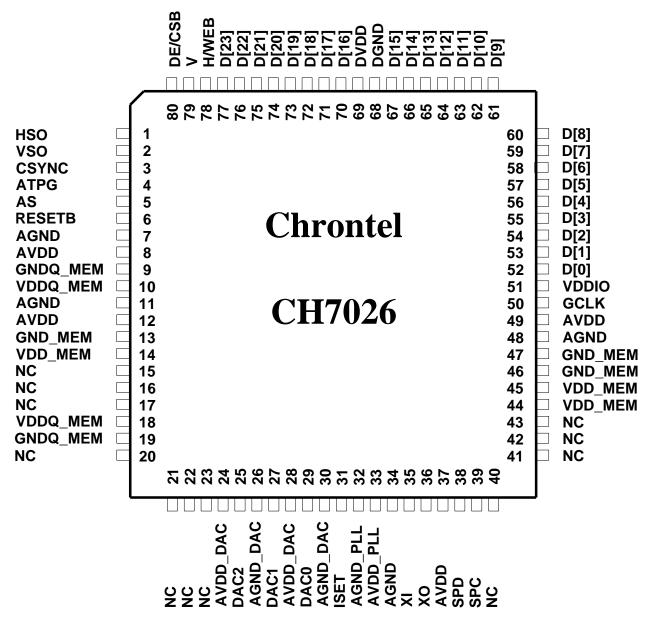

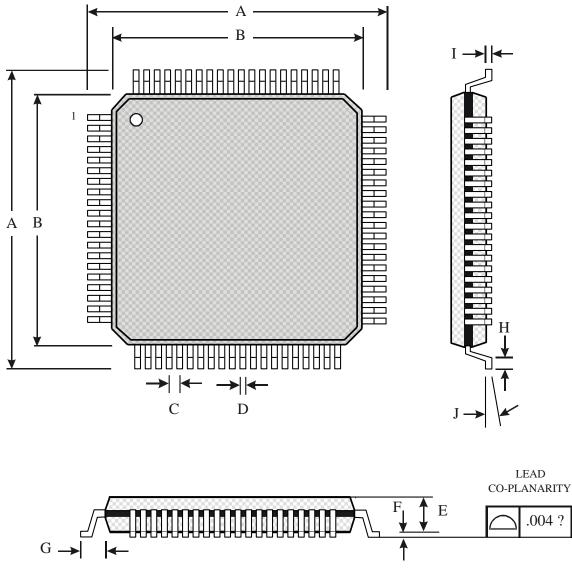

| Figure 2: 80 Pin LQFP Package                                | 5  |

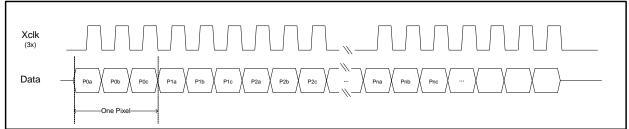

| Figure 3: Clock and Data Input Timing in 3x Multiplexed Mode | 8  |

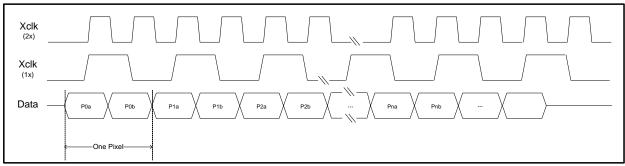

| Figure 4: SDR and DDR Input Data Formats                     |    |

| Figure 5: Horizontal Input Timing                            | 9  |

| Figure 6: Vertical Input Timing                              |    |

| Figure 7: CPU/MEMORY Interface Timing                        |    |

| Figure 8: The Connection of the Serial Port Interface        |    |

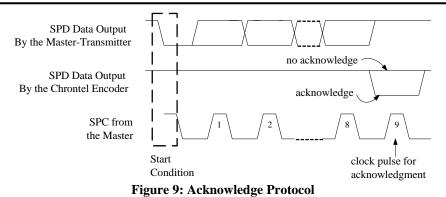

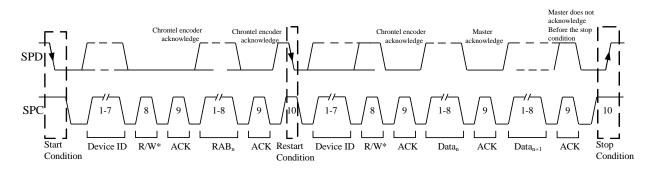

| Figure 9: Acknowledge Protocol                               | 16 |

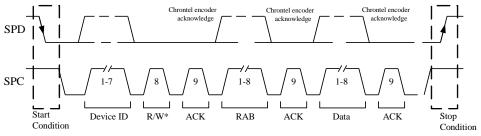

| Figure 10:Single-step Write Cycles (2 cycles)                | 16 |

| Figure 11: Auto-Increment Write Cycle                        | 16 |

| Figure 12: Single-step Read Cycles (2 cycles)                | 17 |

| Figure 13:Auto-increment Read Cycles                         | 17 |

| Figure 14: 80 Pin LQFP Package                               | 21 |

# LIST OF TABLES

| Table 1: Pin Name Descriptions (LQFP80 Package) | 6  |

|-------------------------------------------------|----|

| Table 2: Input Data Format                      | 10 |

| Table 3: Supported SDTV Standards               |    |

| Table 4: Supported EDTV/HDTV Standards          |    |

| Table 5: Composite Sync Type                    |    |

| Table 6: Video DAC Configurations for CH7026    |    |

| Table 7: Test Pattern Selection                 |    |

|                                                 |    |

# **1.0 PIN-OUT**

# 1.1 Package Diagram

Figure 2: 80 Pin LQFP Package

# **1.2** Pin Description

# Table 1: Pin Name Descriptions (LQFP80 Package)

| Pin #   | Туре   | Symbol                 | Description                                                                     |

|---------|--------|------------------------|---------------------------------------------------------------------------------|

| 52 - 67 | In     | D[23:0] <sup>[1]</sup> | Data[0] through Data[23] Inputs                                                 |

| 70 - 77 |        |                        | These pins accept the 24 data inputs from a digital video port of a             |

|         |        |                        | graphics controller. The swing is defined by VDDIO.                             |

| 79      | In/Out | V                      | Vertical Sync Input / Output                                                    |

|         |        |                        | When the SYO control bit is low, this pin accepts a vertical sync input         |

|         |        |                        | for use with the input data.                                                    |

|         |        |                        | When the SYO control bit is high, the device will output a vertical             |

|         |        |                        | sync pulse. The output is driven from the VDDIO supply.                         |

| 78      | In/Out | H/WEB                  | Horizontal Sync Input / Output                                                  |

|         |        |                        | When the SYO control bit is low, this pin accepts a horizontal sync             |

|         |        |                        | input for use with the input data.                                              |

|         |        |                        | When the SYO control bit is high, the device will output a horizontal           |

|         |        |                        | sync pulse. The output is driven from the VDDIO supply.                         |

|         |        |                        | It is also the WEB signal of CPU/MEMORY interface.                              |

| 80      | In     | DE/CSB                 | Data Input Indicator                                                            |

|         |        |                        | When the pin is high, the input data is active.                                 |

|         |        |                        | When the pin is low, the input data is blanking.                                |

|         |        |                        | CSB signal input of CPU/MEMORY interface.                                       |

| 5       | In     | AS                     | Serial Port Device Address Select (7-bit address + R/W bit)                     |

| -       |        | ~                      | 0: 76h                                                                          |

|         |        |                        | 1: 75h                                                                          |

|         |        |                        | B7 B6 B5 B4 B3 B2 B1 B0                                                         |

|         |        |                        | 1 1 1 0 1 AS* AS R/W                                                            |

| 4       | In     | ATPG                   | ATPG Enable (Internally pull-low)                                               |

|         |        |                        | This pin should be left open or pulled low with a 10 k $\Omega$ resistor in the |

|         |        |                        | application. This pin configures the pre-condition for scan chain and           |

|         |        |                        | boundary scan test when high. Otherwise it should be pulled low.                |

|         |        |                        | Voltage level is 0 to 3.3V.                                                     |

| 6       | In     | RESETB                 | Reset * Input                                                                   |

|         |        |                        | When this pin is low, the device is held in the power-on reset                  |

|         |        |                        | condition. When this pin is high, reset is controlled through the serial        |

|         |        |                        | port.                                                                           |

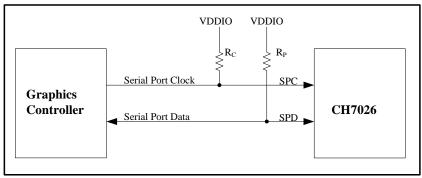

| 38      | In/Out | SPD                    | Serial Port Data Input / Output (open drain)                                    |

|         |        |                        | This pin functions as the bi-directional data pin of the serial port.           |

|         |        |                        | External pull-up resistor is required.                                          |

| 39      | In     | SPC                    | Serial Port Clock Input (open drain)                                            |

|         |        |                        | This pin functions as the clock pin of the serial port. External pull-up        |

|         |        |                        | resistor is required.                                                           |

| 29      | Out    | DAC0                   | CVBS, S-video, YPbPr or Analog RGB output                                       |

|         |        |                        | Full swing is up to 1.3 V                                                       |

| 27      | Out    | DAC1                   | CVBS, S-video, YPbPr or Analog RGB output                                       |

|         |        |                        | Full swing is up to 1.3 V                                                       |

| 25      | Out    | DAC2                   | CVBS, S-video, YPbPr or Analog RGB output                                       |

|         |        |                        | Full swing is up to 1.3 V                                                       |

| 31      | In     | ISET                   | Current Set                                                                     |

|         |        |                        | This pin sets the DAC current. A 1.2 k $\Omega$ , 1% tolerance resistor should  |

|         |        |                        | be connected between this pin and AGND_DAC using short and wide                 |

|         |        |                        | trace.                                                                          |

| 35      | In     | XI                     |                                                                                 |

|         |        |                        |                                                                                 |

|         |        |                        |                                                                                 |

|         |        |                        |                                                                                 |

| 35      | In     | XI                     | · · ·                                                                           |

| 36        | Out   | XO       | Crystal Output                                                                |

|-----------|-------|----------|-------------------------------------------------------------------------------|

|           |       |          | For some situation of the slave mode, a parallel resonance crystal ( $\pm 20$ |

|           |       |          | ppm) should be attached between this pin and XI. However, if an               |

|           |       |          | external CMOS clock is attached to XI, XO should be left open.                |

| 50        | In    | GCLK     | Graphics Controller Clock Input                                               |

| 2         | Out   | VSO      | Vertical sync signal output,                                                  |

|           |       |          | The amplitude of this pin is from 0 to AVDD                                   |

| 1         | Out   | HSO      | Horizontal sync signal output,                                                |

|           |       |          | The amplitude of this pin is from 0 to AVDD                                   |

| 3         | Out   | CSYNC    | Composite sync output,                                                        |

|           |       |          | The amplitude of this pin is from 0 to AVDD                                   |

| 51        | Power | VDDIO    | IO supply voltage (1.2-3.3V)                                                  |

| 69        | Power | DVDD     | Digital supply voltage (1.8V)                                                 |

| 8,12      | Power | AVDD     | Analog supply voltage $(2.5 - 3.3V)$                                          |

| 37, 49    |       |          |                                                                               |

| 33        | Power | AVDD_PLL | PLL supply voltage (1.8V)                                                     |

| 24, 28    | Power | AVDD_DAC | DAC power supply $(2.5 - 3.3V)$                                               |

| 10, 18    | Power | VDDQ_MEM | SDRAM output buffer supply voltage (2.5V)                                     |

| 14, 44    | Power | VDD_MEM  | SDRAM device supply voltage (2.5V)                                            |

| 45        |       |          |                                                                               |

| 68        | Power | DGND     | Digital supply ground                                                         |

| 7, 11, 34 | Power | AGND     | Analog supply ground                                                          |

| 48        |       |          |                                                                               |

| 32        | Power | AGND_PLL | PLL supply ground                                                             |

| 26, 30    | Power | AGND_DAC | DAC supply ground                                                             |

| 9, 19     | Power | GNDQ_MEM | SDRAM output buffer supply ground                                             |

| 13,46, 47 | Power | GND_MEM  | SDRAM device supply ground                                                    |

# Notes:

1. All the unused Data input pins should be pulled low with 10 k $\Omega$  resistors or shorted to Ground directly.

# **2.0 FUNCTIONAL DESCRIPTION**

# 2.1 Input Interface

## 2.1.1 Overview

Five distinct methods of transferring data to the CH7026 are described below.

- 1. Unitary data, clock input at 1X the pixel rate (SDR mode)

- 2. Multiplexed data, clock input at 1X of pixel rate (DDR mode)

- 3. Multiplexed data, clock input at 2X of pixel rate

- 4. Multiplexed data, clock input at 3X of pixel rate

- 5. 8/16/24 bit CPU/MEMORY interface

For the multiplexed data, clock at 1X pixel rate, the data applied to the CH7026 is latched with both edges of the clock (also referred to as dual edge transfer mode or DDR). For the multiplexed data, clock at 2X or 3X pixel rate the data applied to the CH7026 is latched with one edge of the clock (also known as single edge transfer mode or SDR). For the unitary data, clock at 1X pixel rate, the data applied to the CH7026 is latched with one edge of the clock (also known as single edge transfer mode or SDR). For the unitary data, clock at 1X pixel rate, the data applied to the CH7026 is latched with one edge of the clock .The polarity of the pixel clock can be reversed through serial port control. Hsync and Vsync can be input individually or embedded into data signal such as BT656 input format.

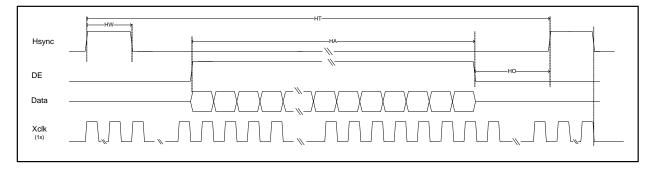

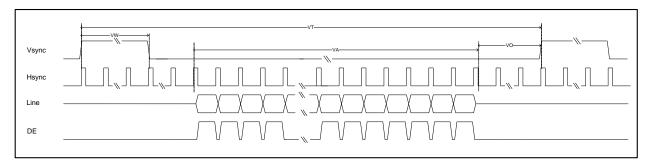

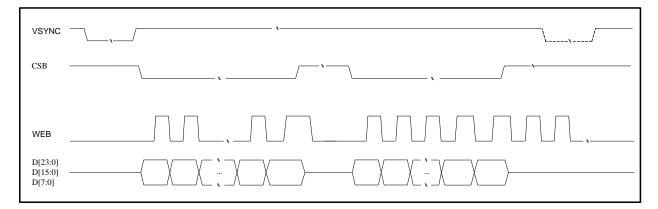

# 2.1.2 Input Clock and Data Timing Diagram

Figure 3 to Figure 7 below shows the timing diagram for input data and clocks. The timing requirements are given in later section.

Figure 3: Clock and Data Input Timing in 3x Multiplexed Mode

Figure 4: SDR and DDR Input Data Formats

(Note: In **Figure 5**, the first XCLK waveform represents the input clock for single edge transfer (SDR) methods. The second XCLK waveform represents the input clock for the dual edge transfer (DDR) method.)

# **Figure 5: Horizontal Input Timing**

# **Figure 6: Vertical Input Timing**

# Figure 7: CPU/MEMORY Interface Timing

(Note: VSYNC pulse of CPU/MEMORY interface is not necessary for each input frame, it is required to appear at least one time at any input frame blank period.)

## 2.1.3 Input Data Voltage

The voltage level of input pins D[23:0], H/WEB, V, DE/CSB are from 0 to VDDIO. These pins support two input mode, one is CMOS mode, the other is pseudo differential mode. The default is CMOS mode with CMOS level on these pins. When control bit **DIFFEN** is high, the input is pseudo differential mode that uses a reference voltage (VREF) to compare with input voltage and decide input logic value. The VREF value can be 80%, 70%, 60% and 50% of VDDIO value, referring to **VRTM[1:0]**. The pseudo differential mode can accept the wide range of the input voltage level from 1.2v to 3.3v, while the CMOS mode can accept 1.8v to 3.3v input voltage.

## 2.1.4 Input Data Format

The following table indicates the supported input data format by CH7026.

# Table 2: Input Data Format

| MULTI IDF      |    | IDF | D[23:16]      | D[15:8]                  | D[7:0]                  |

|----------------|----|-----|---------------|--------------------------|-------------------------|

| 0 0            |    | 0   | R[7:0]        | G[7:0]                   | B[7:0]                  |

|                |    | 1   | 2'b00,R[5:0]  | 2'b00,G[5:0]             | 2'b00,B[5:0]            |

|                |    | 2   | 3'b000,R[4:0] | 2'b00,G[5:0]             | 3'b000,B[4:0]           |

|                |    | 3   | 3'b000,R[4:0] | 3'b000,G[4:0]            | 3'b000,B[4:0]           |

|                |    | 4   | R[7:3],G[7:5] | R[2:0],G[1],G[4:2], B[7] | B[6:3],G[0],B[2:0]      |

|                |    | 5   | 8'h00         | Y[7:0]                   | C[7:0]                  |

|                |    | 6   | 4'h0, Y[9:6]  | Y[5:0],C[9:8]            | C[7:0]                  |

|                |    | 7   | Y[7:0]        | Cb[7:0]                  | Cr[7:0]                 |

|                |    | 8   | Reserved      | Reserved                 | Reserved                |

|                |    | 9   | 6'h00, R[5:4] | R[3:0],G[5:2]            | G[1:0],B[5:0]           |

|                |    | 10  | 8'h00         | R[4:0],G[5:3]            | G[2:0],B[4:0]           |

|                |    | 11  | 8'h00         | 1'b0, R[4:0],G[4:3]      | G[2:0],B[4:0]           |

| 1              | PA | 0   |               | 4'h0, R[7:4]             | R[3:0],G[7:4]           |

|                | PB |     |               | 4'h0, G[3:0]             | B[7:0]                  |

| PA             |    | 1   |               | 7'h00, R[5]              | R[4:0],G[5,3]           |

|                | PB |     |               | 7'h00, G[2]              | G[1:0],B[5:0]           |

| PA             |    | 2   |               |                          | R[4:0],G[5,3]           |

|                | PB |     |               |                          | G[2:0],B[4:0]           |

|                | PA | 3   |               |                          | 1'b0,R[4:0],G[4,3]      |

|                | PB |     |               |                          | G[2:0],B[4:0]           |

| PA<br>PB<br>PA |    | 4   |               | 4'h0, R[7:4]             | R[3],G[7:5],R[2:0],G[1] |

|                |    |     |               | 4'h0, G[4:2], B [7]      | B[6:3],G[0],B[2:0]      |

|                |    | 5   |               |                          | Y[7:0]                  |

|                | PB |     |               |                          | C[7:0]                  |

|                | PA | 6   |               | 6'h00, Y[9:8]            | Y[7:0]                  |

|                | PB |     |               | 6'h00, C[9:8]            | C[7:0]                  |

|                | PA | 7   |               | 4'h0, Y[7:4]             | Y[3:0],Cb[7:4]          |

|                | PB |     |               | 4'h0, Cb[3:0]            | Cr[7:0]                 |

| 2              | PA | 0   |               |                          | R[7:0]                  |

|                | PB |     |               |                          | G[7:0]                  |

|                | PC |     |               |                          | B[7:0]                  |

|                | PA | 7   |               |                          | Y[7:0]                  |

|                | PB |     |               |                          | Cb[7:0]                 |

|                | PC |     |               |                          | Cr[7:0]                 |

(PA,PB,PC represent the parts of one pixel data)

IDF[3:0] describes the major input data format that CH7026 accepts. They are:

IDF = 0: 888 RGB(standard order) input

IDF = 1: 666 RGB input

IDF = 2: 565 RGB input

IDF = 3: 555 RGB input

IDF = 4: 888 RGB(special order) input

IDF = 5: 8-bit YCbCr4:2:2 input IDF = 6: 10-bit YCbCr4:2:2 input IDF = 7: 8-bit YCbCr4:4:4 input IDF = 8: Reserved IDF = 9: Consecutive aligned 666 RGB input IDF = 10: Consecutive aligned 565 RGB input IDF = 11: Consecutive aligned 555 RGB input

**Table 2** above describes the 24-bit input data format under unitary mode. For multiplexed input, input data need to be de-multiplexed to unitary input first then this table can be applied. The Pixel Data bus represents a 12-bit or 8-bit multiplexed data stream, which contains either RGB or YCbCr formatted data. The input data rate is 2X the pixel

rate, and each pair of Pn values (e.g.; PA and PB) contains a complete pixel (3X input has the similar feature).

When the input is a YCbCr data stream the color-difference data will be transmitted at half the data rate of the luminance data, with the sequence being set as Cb, Y, Cr, Y, where Cb0,Y0,Cr0 refers to co-sited luminance and color-difference samples and the following Y1 byte refers to the next luminance sample, per ITU-R BT.656 standards (the clock frequency is dependent upon the current mode, and is not 27MHz as specified in ITU-R BT.656). In YCbCr 4:2:2 with embedded sync mode, the hardware can detect the connection error and correct it automatically.

# 2.2 Chip Output

# 2.2.1 TV Output

The CH7026 supports the following output formats:

| No. | Standards     | Field Rate<br>(Hz) | Total   | Scan Type  |

|-----|---------------|--------------------|---------|------------|

| 0   | NTSC-M        | 60/1.001           | 858x525 | Interlaced |

| 1   | NTSC-J        | 60/1.001           | 858x525 | Interlaced |

| 2   | NTSC-443      | 60/1.001           | 858x525 | Interlaced |

| 3   | PAL-B/D/G/H/I | 50                 | 864x625 | Interlaced |

| 4   | PAL-M         | 60/1.001           | 858x525 | Interlaced |

| 5   | PAL_N         | 50                 | 864x625 | Interlaced |

| 6   | PAL-Nc        | 50                 | 864x625 | Interlaced |

| 7   | PAL_60        | 60/1.001           | 858x525 | Interlaced |

#### Table 3: Supported SDTV Standards

## Table 4: Supported EDTV/HDTV Standards

| Standards |           | Field/Frame Rate (Hz) | Total      | Active    | Clock (MHz) | Scan Type   |

|-----------|-----------|-----------------------|------------|-----------|-------------|-------------|

| 480/60p   | SMPTE293M | 60/1.001              | 858x525 or | 720x480   | 27 or 54    | Progressive |

|           | EIA770.2A |                       | 1716x525   |           |             |             |

| 576/50p   | ITU-R     | 50                    | 864x625 or | 720x576   | 27 or 54    | Progressive |

|           | BT1358    |                       | 1728x625   |           |             |             |

| 720/60p   | SMPTE296M | 60 or 60/1.001        | 1650x750   | 1280x720  | 74.25 or    | Progressive |

|           |           |                       |            |           | 74.176      |             |

| 720/50p   | SMPTE296M | 50                    | 1980x750   | 1280x720  | 74.25       | Progressive |

| 1080/60i  | SMPTE274M | 60 or 60/1.001        | 2200x1125  | 1920x1080 | 74.25 or    | Interlaced  |

|           |           |                       |            |           | 74.176      |             |

| 1080/50i  | SMPTE274M | 50                    | 2640x1125  | 1920x1080 | 74.25       | Interlaced  |

| 1080/50i  | SMPTE295M | 50                    | 2376x1250  | 1920x1080 | 74.25       | Interlaced  |

CVBS, S-video, YPbPr and analog RGB output are supported, when output analog RGB, composite sync output is available.

# 2.2.2 VGA Output

CH7026 also supports analog RGB output through video DACs. Typically used resolution are 800x600, 856x480, 800x480 or 640x480. Vertical sync and horizontal sync signal are provided. Composite sync output is also supported. The type of composite sync can be programmed through register map.

| CSSEL[2:0] | Composite sync type |

|------------|---------------------|

| 0          | Vsync XOR Hsync     |

| 1          | Vsync OR Hsync      |

| 2          | Vsync AND Hsync     |

#### Table 5: Composite Sync Type

#### 2.2.3 Video DAC Output

The DAC output is configured by the register bits **VFMT[2:0]**. **DACS[1:0]** bits are used to control the multiple output format i.e. dual or triple CVBS output, dual CVBS and S-Video output and etc. **DACSP[2:0]** bits are to swap the DAC output sequence such as CVBS, S-Video or S-Video, CVBS. Detailed information of these bits are described in register bits description section of this document. **Table 6** below lists the DAC output configurations of the CH7026:

#### Table 6: Video DAC Configurations for CH7026

| DAC0 | DAC1  | DAC2  |

|------|-------|-------|

| CVBS | Y     | С     |

| CVBS | CVBS  | 0     |

| CVBS | CVBS  | CVBS  |

| Y(R) | Pb(G) | Pr(B) |

## 2.2.4 DAC Single/Double Termination

The DAC output of CH7026 can be single terminated or double terminated. Using single termination will save power consumption while double termination is likely to minimize the reflection from the cable. Refer to the description of register bit **SEL\_R**.

## 2.2.5 Video DAC Connection Detect

CH7026 can detect the Video DAC connection by setting register SPPSNS. It can detect which DAC is connected, short to ground or not connected.

## 2.2.6 Picture Enhancement

The CH7026 has the capability of vertical and horizontal output picture position adjustment. It can automatically put the picture in the display center, and the vertical or horizontal position is also programmable through user input. And also it can provide brightness, contrast, hue, saturation adjustment and text enhancement functions. (For analog RGB output, only brightness and contrast adjustment are available).

CH7026 also supports vertical or horizontal flip and rotation (0, 90, 180 and 270 degree) functions.

# 2.2.7 Color Sub-carrier Generation

CH7026 has two ways to generate the color sub-carrier frequency. If the **GCLK** from the graphics controller has a steady center frequency and very small jitter, the sub-carrier can be derived from the **GCLK**. However, since even a  $\pm 0.01\%$  sub-carrier frequency variation is enough to cause some TV to lose color lock, CH7026 has the ability to generate the sub-carrier frequency from the crystal when the **GCLK** from the graphics device cannot meet the requirement. In this case, the crystal has to be present.

# CHRONTEL

In addition, CH7026 has the capability to gen-lock the color sub-carrier with Vsync. Also, it has the ability to operate in a "stop dot crawl" mode for NTSC CVBS output when the first sub-carrier generation method is used.

# 2.2.8 ITU-R BT.470 Compliance

The SDTV output of CH7026 is mostly compliant with ITU-R BT.470 standard except for the items below.

- The frequencies of horizontal sync, vertical sync, and color sub-carrier depend on the quality of **GCLK** from graphics controller and/or the off-chip crystal.

- It is assumed that gamma correction, if required, is performed in the graphics device.

- Pulse widths and rise/fall times for sync pulses, front/back porches, and equalizing pulses are designed to approximate ITU-R BT.470 requirements. However, they may have a small variation depending on the actual input and output format.

- The actual bandwidths of the luminance and chrominance signals depend on the input resolution and the filter selection.

# 2.3 Testing Functions and Power Down Mode

## 2.3.1 Test Pattern Select

Setting TSTP[3:0] of 04h on the second page of register map can select different video patterns that go through datapath, according to the following table. TEST (bit5 of 04h on the second page) has to be 1 to enable test mode. TSYNC is to select which sync will be used internally generated sync or external input sync.

| TSTP[3:0] | Test pattern             |

|-----------|--------------------------|

| 0         | Black                    |

| 1         | White                    |

| 2         | Vertical ramp            |

| 3         | Horizontal ramp          |

| 4         | Color bar                |

| 5         | One pixel wide color bar |